Connect Your Core To The CXL World

PCIe Controller IP

Technology

PCIe Controller IP

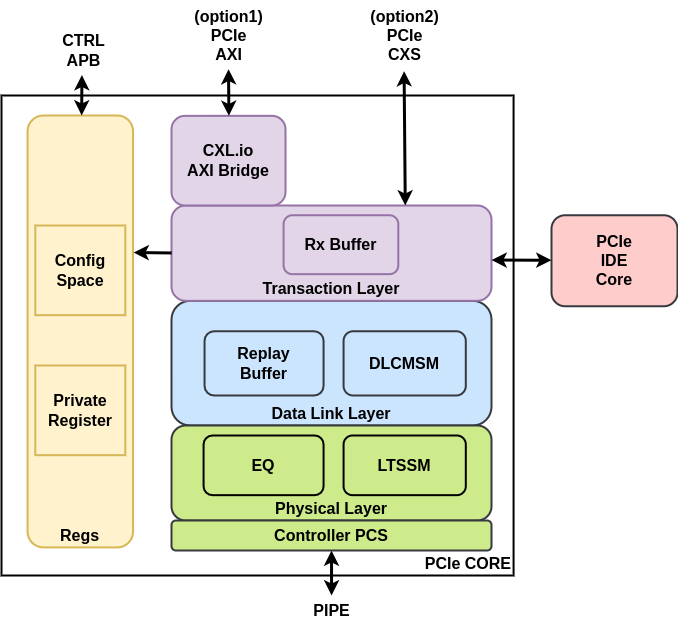

The Wolley PCI Express® (PCIe®) Controller IP is a highly configurable, performance-optimized core designed for ASIC and FPGA integration. Supporting PCIe Gen1 throughGen6 at data rates up to 64 GT/s, the controller accommodates a wide range of linkwidths (x1–x16) and protocol features to meet the demands of next-generation SoC,networking, and high-performance computing platforms. The controller seamlesslyinteroperates with PIPE-compliant PHYs and supports multiple modes including RootComplex, Endpoint, Switch, and Dual-Mode operation.

Engineered for scalability and low latency, the design is verified across emulation, FPGA,and silicon environments, and integrates rich RAS features, power optimizationtechniques, and AXI-based interfaces for system compatibility.

Key Features

- Compliant with PCIe 6

- Compliant with PIPE 6.x

- Support FLIT and non-FLIT modes

- Multi-mode operation: Root Complex, Endpoint, Dual-Mode, and Switch

- Flexible core data path: Configurable 256b, 512b, and 1024b core data width

- Support AXI4 and native TLP interface

- RAS features: Timer overrides, error injection, LTSSM debug, ACK/NAK timers

- Low Power Modes: L0p, L1, L1 Substates

- IDE (Integrity and Data Encryption) optional security module

- Support SRIS mode

- Support multiple virtual channels (VCs)

Benefits

- Broad application fit through support for full PCIe generations and configurations

- Highly scalable architecture to meet bandwidth, power, or area requirements

- Fast time-to-market enabled by thorough verification across multiple platforms

- Configurable datapath and logic reduce gate count for targeted deployments

- Support optional integrity and Data Encryption (IDE)

Applications

Data Center and Edge AI Accelerators; High-performance Computing (HPC); NetworkInterface Cards (NICs); Enterprise-grade FPGA Solutions; NVMe